随着数据中心对存储密度与计算效率的要求不断提升,传统 U.2 接口在空间利用和扩展性上逐渐显现出局限。在此背景下,MCIO(Multi-Channel Input/Output) 作为一种高密度、多通道的物理连接标准,正在被 Intel、AMD 等主流平台广泛采纳。

1. 什么是 MCIO?

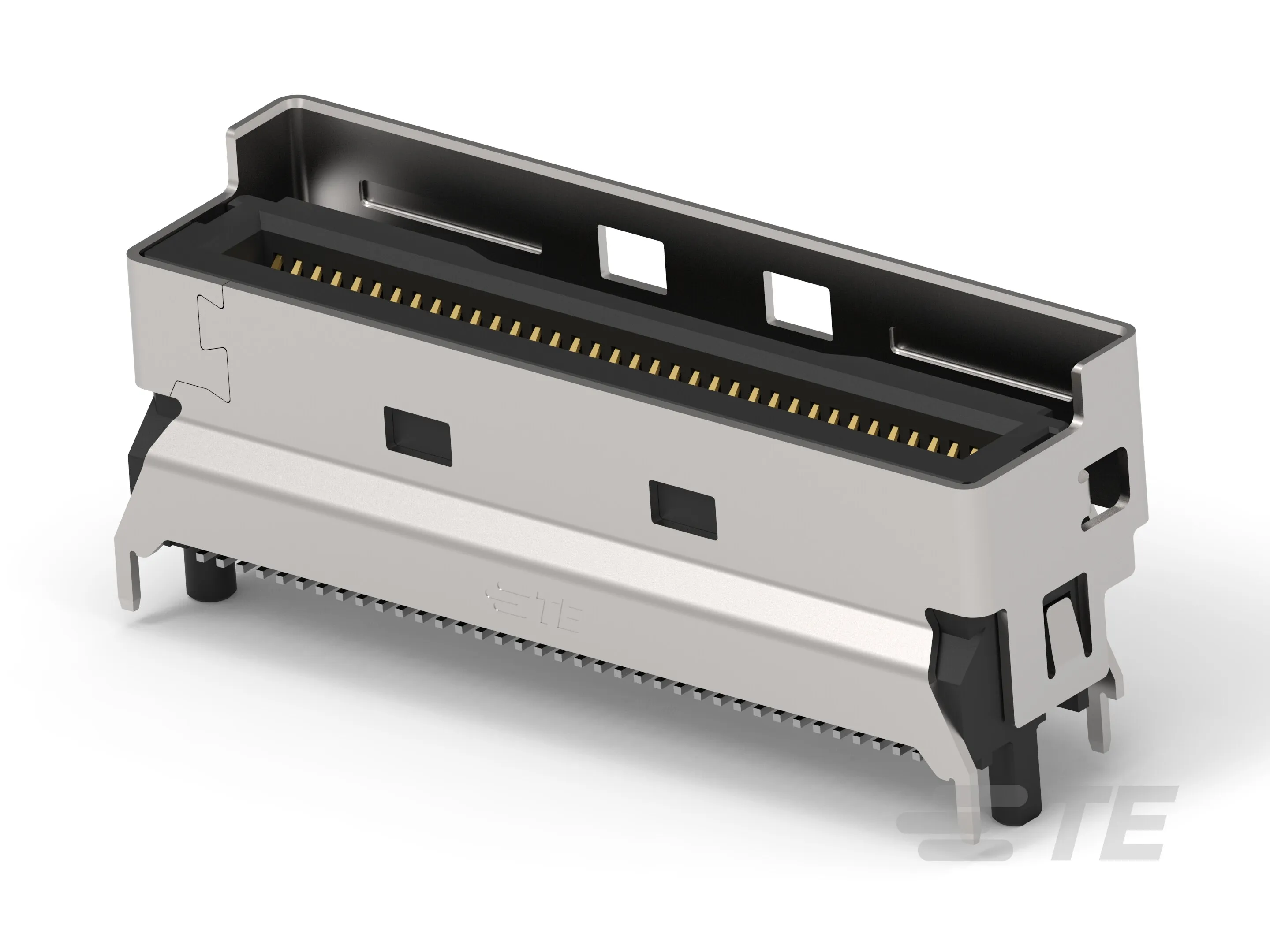

MCIO 并非通信协议,而是一种物理层接口规范,由 SFF-TA-1045 标准定义。它通过一个紧凑型连接器(通常为 74-pin 或 98-pin),支持多达 16 条 PCIe 通道,可同时驱动多个 NVMe SSD 或加速设备。

2. 核心应用场景

- 企业级 NVMe 存储扩展:单个 MCIO 接口可连接 2~4 块 E1.S SSD,大幅提升机箱内存储密度。

- AI 训练服务器互联:用于 GPU 与智能 SSD 之间的直连,减少 CPU 中转,降低延迟。

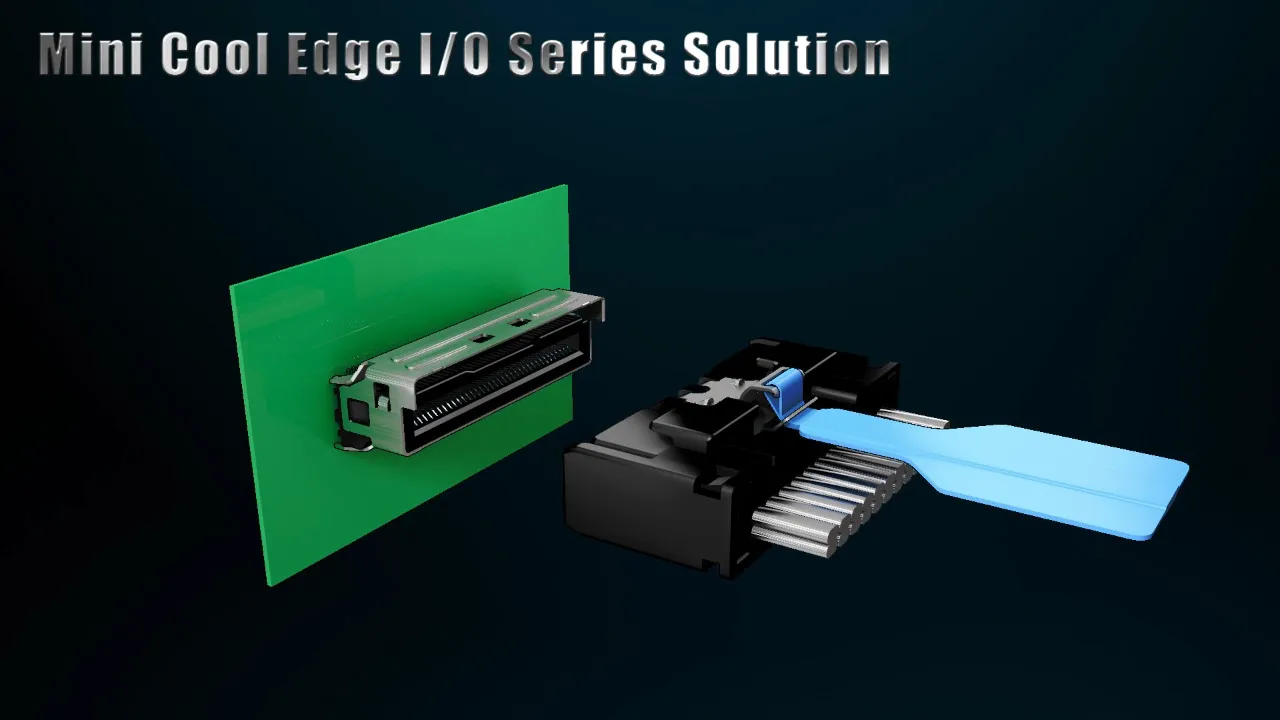

- 边缘计算节点:紧凑型设计完美匹配微型服务器对空间与性能的双重需求。

3. 关键技术参数

| 参数 | 规格 |

|---|---|

| 物理接口 | SFF-TA-1045 定义的 MCIO 连接器(74-pin / 98-pin) |

| 支持协议 | PCIe Gen4 / Gen5 + NVMe |

| 最大通道数 | 16 条(4× x4 配置) |

| 单通道速率 | 最高 32 GT/s(PCIe Gen5) |

| 兼容性 | 可通过转接板支持 U.2/U.3 设备 |

4. 发展路径与未来趋势

MCIO 自 2020 年随 Intel Ice Lake-SP 平台首次亮相,如今已进入生态成熟期:

- 2023–2024:AMD EPYC 平台全面支持,推动行业统一。

- 2025+ :随着 CXL(Compute Express Link)普及,MCIO 有望集成内存池连接能力,成为异构计算的物理基石。